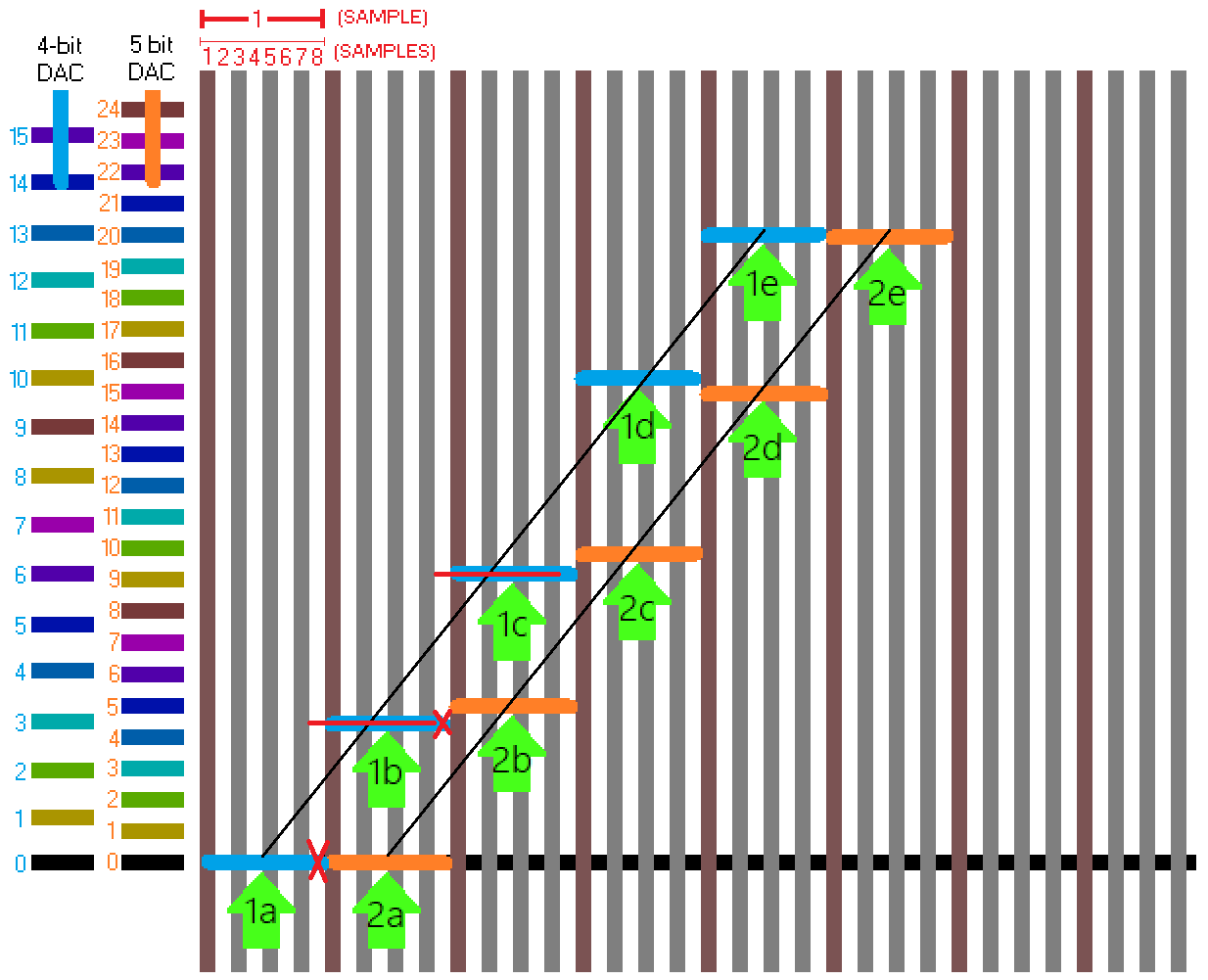

I spent some time in paint to contrast a 4 and 5 bit DAC doing the same thing, then the 4 bit DAC with 8x oversampling (increasing its resolution by 1.5 bits, woo!)

Did I do it right?

(yes, it's all+ lol... this ain't music! Just a rising voltage...)

It took me a little while to think over how I was going to do this, then arranging it, counting the pixels for proper spacing so it actually made a bit of sense... (the 5 bit DAC was the perfect device to capture the rising voltage, and perfectly in phase, too! If my brain didn't let me down I probably would've done 5 and 6 bit and just not shown the bottom half... NEXT TIME! lol)

I labelled things so that it's easier to discuss, get clarification, or point out problems

In case it's not obvious, the red-brown vertical lines are the 1x sample rate, and the brown, white, grey, white, grey, white, grey, white are 1, 2, 3, 4, 5, 6, 7, 8 samples for the 8x.

The blue lines are the 4 bit DAC originally, and the thin red lines over the blue lines are the 8x oversample (corrected) position. When there are no red lines, the blue lines are the red lines, and when the red x is over blue line, it's because the red line has taken its place.

(BTW the black lines are exact to the pixel precision - starting in the same spot (top center) in 1a/2a, and finishing in the top center of 2e, but not 1e, because the 4 bit DAC's 13th step is slightly higher than the 5 bit DAC's 20th)

Is this also how delta-sigma DACs work? Just running at many many many MHz?

Or is this a horrible failing - go back to grade 1 and stay there for 2 years Michael. No recess, no lunch, and 2 hours of homework for every hour you were in school during the day!

Did I do it right?

(yes, it's all+ lol... this ain't music! Just a rising voltage...)

It took me a little while to think over how I was going to do this, then arranging it, counting the pixels for proper spacing so it actually made a bit of sense... (the 5 bit DAC was the perfect device to capture the rising voltage, and perfectly in phase, too! If my brain didn't let me down I probably would've done 5 and 6 bit and just not shown the bottom half... NEXT TIME! lol)

I labelled things so that it's easier to discuss, get clarification, or point out problems

In case it's not obvious, the red-brown vertical lines are the 1x sample rate, and the brown, white, grey, white, grey, white, grey, white are 1, 2, 3, 4, 5, 6, 7, 8 samples for the 8x.

The blue lines are the 4 bit DAC originally, and the thin red lines over the blue lines are the 8x oversample (corrected) position. When there are no red lines, the blue lines are the red lines, and when the red x is over blue line, it's because the red line has taken its place.

(BTW the black lines are exact to the pixel precision - starting in the same spot (top center) in 1a/2a, and finishing in the top center of 2e, but not 1e, because the 4 bit DAC's 13th step is slightly higher than the 5 bit DAC's 20th)

Is this also how delta-sigma DACs work? Just running at many many many MHz?

Or is this a horrible failing - go back to grade 1 and stay there for 2 years Michael. No recess, no lunch, and 2 hours of homework for every hour you were in school during the day!